ULTRA300 RH

FPGAs Radiation Hardened

ULTRA300 is the second generation of NanoXplore Radiation Hardened by design (RHBD) FPGA.

The hardening technics used in the Ultra300 family alongside the FD-SOI technology offers very strong hardening performance.

Security

Embedded protection by design, for mission-critical confidence

Reliability

Proven resilience for the harshest environments, from orbit to the edge

Performance

Scalable performance and flexibility to meet all your system’s needs

Technical specifications

Detailled specifications to ensure optimal performance in every environment

| Device | NX2H300TSA |

|---|---|

| Capacity | |

| - ASIC Gates | 4 000 000 |

| Logic Modules | |

| - Register | 273 408 |

| - LUT-4 | 290 496 |

| - Carry | 68 352 |

| Embedded RAM | 22Mb |

| - DPRAM | 21504 |

| - Core Register File | 1424 |

| Clocks / PLL | 50/7 |

| Additional Features | |

| - SpaceWire PHY (8 IOBs) | 20 |

| - DDR3/4 PHY (11 IOBs) | 20 |

| - Embeded DSP | 896 |

| - DSP Blocks | 1 |

| - SpaceWire link I/F 400Mbps | 16 |

| - SERDES Tx/Rx 12,5Gbps BGA1152 BGA484 | 16 4 |

| - Hard IP Processor core / SoC | NO |

| - ADC / DAC | 4 / 4 |

| Design Security | YES |

| Inputs / Outputs | |

| - Complex I/O bank | 10x 34 I/Os |

| - Simple I/O bank | 1x 16 I/Os + 6x 24 I/Os |

| Packages - User I/Os | 500 I/Os |

| - BGA484 27*27mm / 1mm User IOs | 239 |

| - BGA1152 35*35mm / 1mm User IOs | 500 |

Radiation Hardened

Radiation hardening by design in configuration memories and registers

SEU immune up to LET > 60MeV.cm2/mg

Total ionizing dose > 50Krads (Si)

Embedded EDAC for user memory mitigation

Embedded configuration memory scrubbing

Fast automatic memory configuration repair

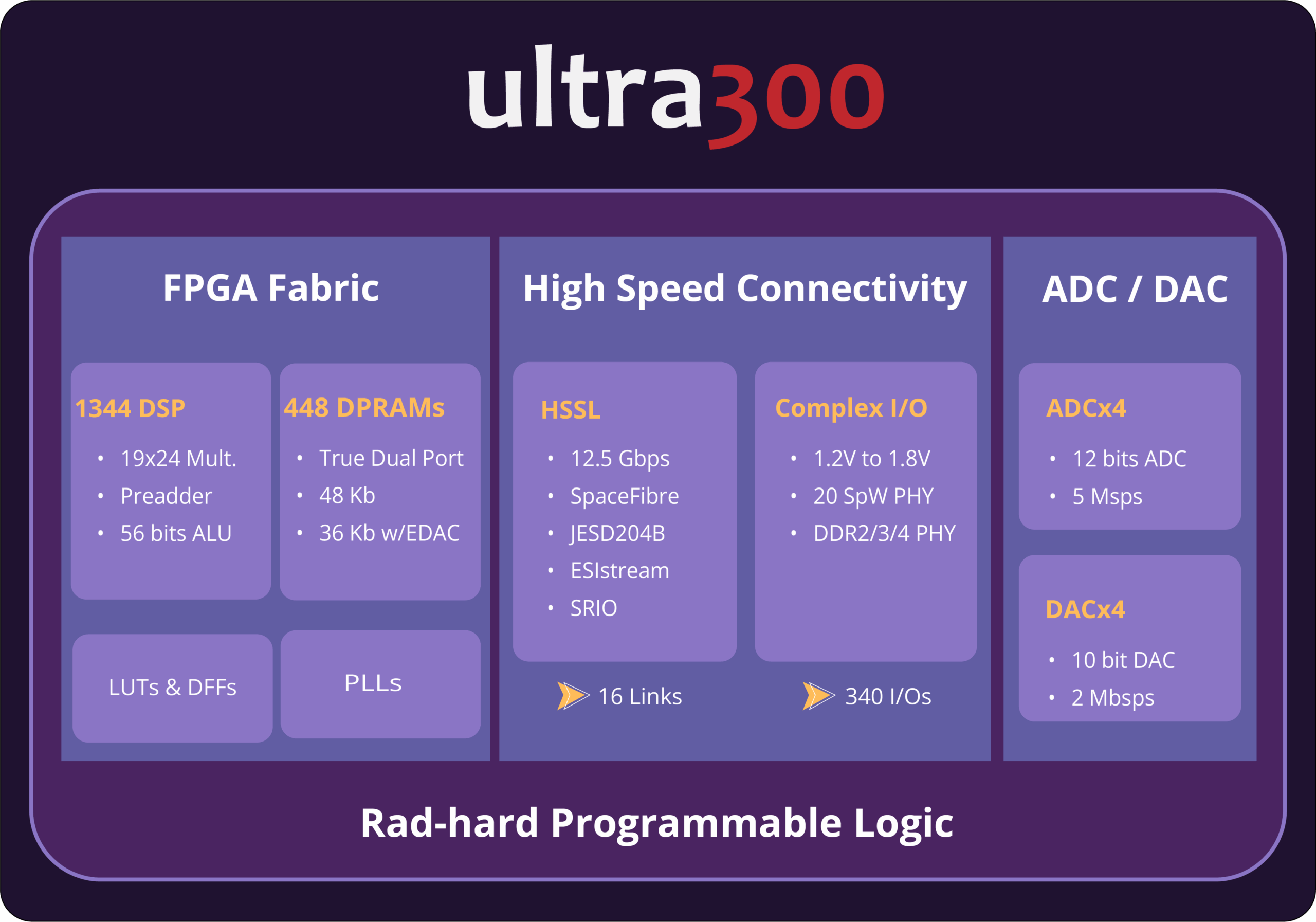

Main Features

28 nm STMFDSOI process technology

A full System-On-Chip (SoC) based on a quad-core ARM Cortex R52

4-Input Look-up tables

LUT expander to support up to 16 bits boolean functions

High performance carry chains

Advanced interconnect network to support random logic and coarse grain block functions

DSP Blocks for complex arithmetic operations

User memories with variable width and depth

Configuration modes: Master Serial SPI (Single, Sequential, TMR), SpaceWire

Development configuration modes: JTAG, Parallel 16 bits, UART

Integrated Space Wire interface available for user applications

Dedicated lowskew distribution network for clock, reset and load enable signals

On-chip thermal sensor and monitoring capability

Input / Output Features

Multiple I/O powering support from 1.2V to 3.3V

Cold sparing support.

Programmable output drive to support multiple industry standards.

Embedded logic to support DDR2, DDR3.

Up to 1.6 Gbps maximum I/O support for SSTL, HSTL and POD standards.

LVDS compatible mode.

All pins support 2000V of ESD-HBM.

Embedded logic to support Space Wire Data Strobe encoding.

Programmable delay lines on complex I/O pins.

Programmable resistive termination on complex I/O pins.

Documentation

Guiding your project from concept to long term success

For a complete library of user guides, reference manuals and technical documentation,

or if you have an questions about our products, head to our Wiki Page.

Product Brief

Download the complete overview

Detailed architecture, radiation performance and full technical specifications.

Related products

Discover our other products.

- Tools

Impulse Design Suite

Impulse is NanoXplore's design and development suite for its Radiation-Hardened FPGA portfolio. It provides a complete design - FPGAs Radiation Hardened

ULTRA300

ULTRA300 is the commercial version of NanoXplore’s second-generation FPGA family. It shares the same programmable architecture - Radiation Hardened SoC FPGAs

NG-ULTRA

NG-ULTRA share the same patented FPGA architecture co-developed with ST, combining programmable logic with embedded quad-core - FPGAs Radiation Hardened

NG-MEDIUM

NG MEDIUM is an SRAM-based FPGA developed by NanoXplore, sharing the same programmable architecture as the